|

|

|

| HOME | DOWNLOAD | DOCUMENTATION | COLLABORATIONS | PUBLICATIONS | SCICOS/SynDEx | SynDEx-IC |

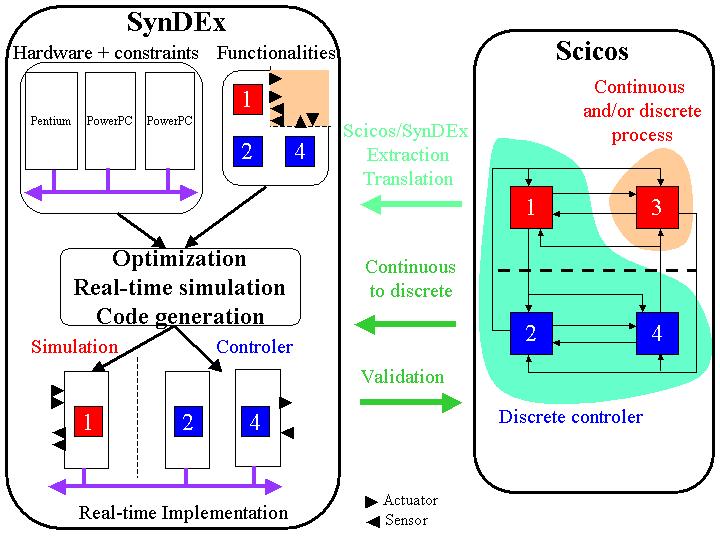

Scicos to SynDEx gatewayContextThe Scicos/SynDEx gateway was formerly developped inside the ECLIPSE RNTL project (2003-2005) whose PSA was the main industrial partner. It is presently maintained and developed in the AOSTE INRIA project-team. ObjectivesThe Scicos and SynDEx softwares are based on different formalisms. Scicos is a graphical architecture-independent dynamical system modeler and simulator toolbox included in the Scicoslab engineering and scientific computation software, whereas SynDEx is a system level CAD software for prototyping and optimizing the implementation of distributed real-time embedded applications onto "multicomponent" architectures. A semantic gap between the two softwares prevents a direct translation from a Scicos model to a SynDEx one. The Scicos/SynDEx gateway provides a way to convert a Scicos model into a SynDEx one allowing the implementation of a model specified with Scicos onto a multiprocessor architecture via SynDEx while verifying real-time constraints. Once the model is implemented, i.e. distributed and scheduled onto the target architecture, the user can automatically generate a safe and optimized real-time code which runs and run on the specified architecture. Then, the user can compare the results obtained during the Scicos simulation with those obtained during the real-time execution, and consequently modify the initial Scicos dynamical model if needed. The development processA user wishing to develop and implement a dynamical model onto a target architecture must go through the following steps:

The figure below presents the complete development process from the Scicos modeling to the real-time multiprocessor execution onto the target architecture.

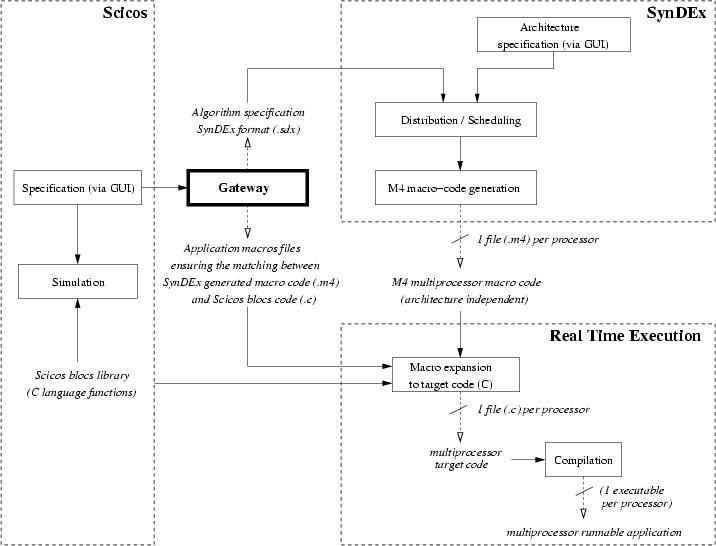

Gateway principlesThe figure below shows how the Scicos To SynDEx gateway interacts with Scicos and SynDEx.

More precisely, the gateway provides the following functionalities:

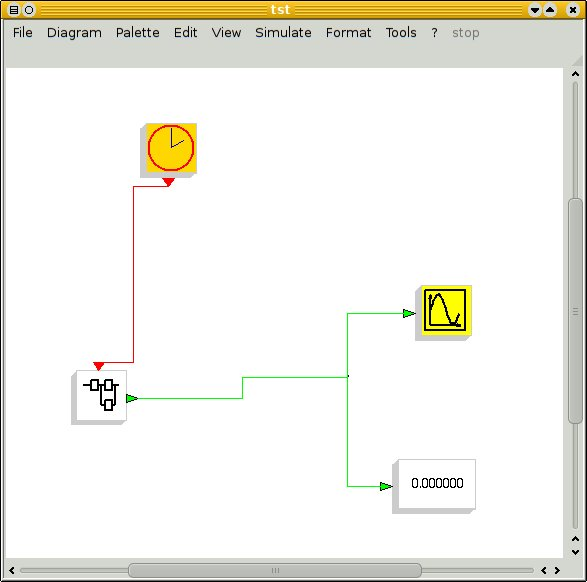

How to use itThe gateway allows the user to translate any Scicos superbloc with one activation input port (synchronous), no activation output port and any number of data input/output ports. The figure below shows some eligible superblocs.

When a superbloc has been fully specified with Scicos, the user just has to:

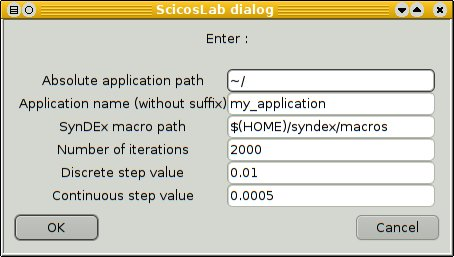

Once the translation process is over, a pop-up window asks the user to specify some parameters.

The .sdx and .m4 files are then generated into the user specified path and can be processed by SynDEx. Installation

Last update: November 5th 2016 For any question, please contact: Yves.Sorel@inria.fr |